em-III-CBSGS/EXTC/Analog Electronics-I/ May-2016

QP Code: 30569

(3 Hours)

[ Total Marks: 80

20

- (1) Question No. 1 is compulsory.

- (2) Attempt any three questions out of remaining five questions.

- (3) Assume suitable data if required and mention the same in answer sheet.

Attempt any five questions :-

Find V<sub>E</sub> and I<sub>E</sub> for the circuit given below.

270 Kg | BE100

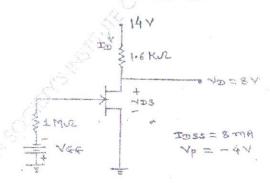

(b) For the circuit given below find I, VDs, VGG

- Write down current equation of diode and explain significance of each parameters.

- Explain the concept of thermal runaway in BJT.

Con. 9416-16.

TURN OVER

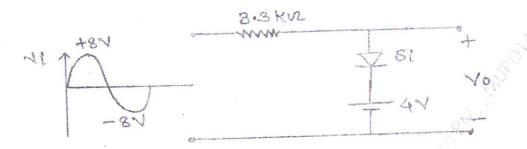

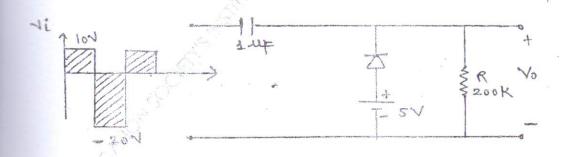

(e) Draw the output Waveform Vo for circuit shown.

- (f) State and explain Barkhausen's criteria for oscillations.

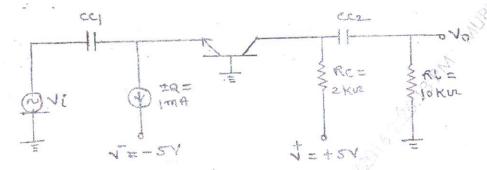

- 2. (a) Determine Q-Print and draw d.c. load line for the amplifier shown.

(b) Derive the expression for frequency of oscillation for a BJTRC phase shift oscillator.

TURN OVER

10

-W-Con. 9416-16.

## QP Code: 30569

-3-

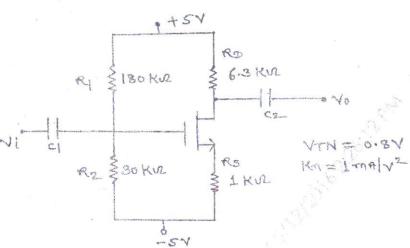

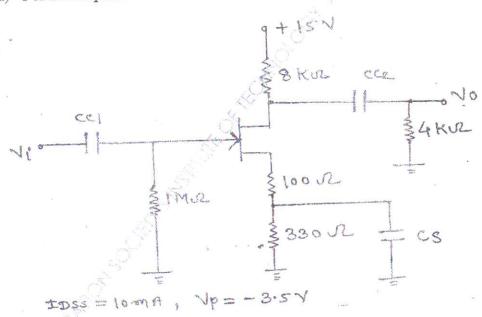

(a) Determine voltage gain, Input resistance and output resistance for the MOSFET amplifier shown.

- (b) Explain the working and characteristics of n-channel Junction Field Effect

Translators (JFET)

- (a) Draw the output waveform V<sub>0</sub> for ckt shown if (i) Vr = 0V (ii) Vr = 0.7v where Vr is cutin voltage of diode.

[TURN OVER

FM-Con.9416-16.

10

10

10

(b) For the common base circuit shown, the transistor has parameters  $\beta = 120$  and  $V_A = \infty$

(i) Determine the quiescent V<sub>CEQ</sub>

(ii) Determine the small signal voltage gain and output resistance.

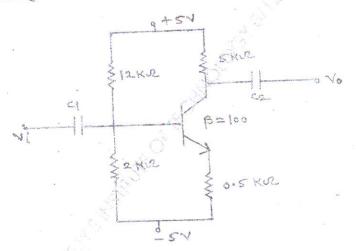

5. (a) For the Amplifier shown determine (i) Q point (ii) Av, Zi, Zo

TURN OVER

FW-Con. 9416-16.

QP Code: 30569

-5-

(b) Derive expressions for voltage gain, input resistance and output resistance for source follower circuit using n-channel MOSFET.

## Write short notes on any Four :-

- (i) Construction and operation of varactor diode

- (ii) MOS capacitor

10

- (iii) Transistor as a switch

- (iv) Crystal oscillator

- (v) Hybrid-π model of BJT

FW-Con. 9416-16.

3. E. Sem III (Extc) CBEGS.

QP Code: 30666

Digital Electronies

(3 Hours)

Max Marks: 80

| 1. | Que | estion | No. | 1 | is | compulsory | 7. |

|----|-----|--------|-----|---|----|------------|----|

|    |     |        |     |   |    |            |    |

- 2. Out of remaining questions, attempt any three questions.

- 3. Assume suitable additional data if required.

- 4. Figures in brackets on the right hand side indicate full marks.

| 1. | (A)        | Compare Combinational circuits with Sequential circuits.                                                                                                                             | (05) |

|----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|    | (B)        | Compare Synchronous with Asynchronous counter.                                                                                                                                       | (05) |

|    | (C)        | Compare TTL with CMOS logic families.                                                                                                                                                | (05) |

|    | (D)        | Compare PLA with PAL.                                                                                                                                                                | (05) |

| 2. | (A)        | Write the VHDL code for 2-bit up-down counter with positive edge triggered clock.                                                                                                    | (10) |

|    | <b>(B)</b> | State and prove the De Morgan's theorem.                                                                                                                                             | (05) |

|    | (C)        | Draw the block diagram of internal architecture of XC4000 family FPGA.                                                                                                               | (05) |

| 3. | (A)        | Design synchronous counter using T-type flip flops for getting the following sequence: $0 \rightarrow 2 \rightarrow 4 \rightarrow 6 \rightarrow 0$ . Take care of lockout condition. | (10) |

|    | (B)        | Convert T-type flip flop into D-type flip flop.                                                                                                                                      | (05) |

|    | (C)        | Write (AB) <sub>16</sub> into its BCD code and Octal code.                                                                                                                           | (05) |

| 4. | (A)        | Implement the following Boolean equation using single 4:1 MUX and few logic gates: $F(P,Q,R,S) = \prod M(0,2,5,6,7,9,12,15)$ .                                                       | (10) |

|    |            |                                                                                                                                                                                      |      |

|    | (B)        | Compare FPGAs with CPLDs.                                                                                                                                                            | (05) |

|    | (C)        | Implement $Y = A + \overline{B}C$ using only NOR gates.                                                                                                                              | (05) |

| 5. | (A)        | Draw a neat circuit of BCD adder using IC 7483 and explain.                                                                                                                          | (10) |

|    | <b>(B)</b> | Using Quine McClusky method, minimize the following:                                                                                                                                 | (10) |

|    |            | $F(P,Q,R,S) = \sum m(0,1,3,7,8,9,15) + d(2,10,11).$                                                                                                                                  |      |

|    |            |                                                                                                                                                                                      |      |

| 6. | (A)        | Design a Mealy type sequence detector circuit to detect a sequence 1101 using T-type flip flops.                                                                                     | (10) |

|    | (B)        | What is shift register? Explain any one type of shift register. Give its application.                                                                                                | (10) |

FW-Con.: 11014-16.

QP Code: 30754

(3 Hours)

[ Total Marks: 80

5

5

- (1) Attempt questions No. 1 and any 3 from remaining questions. In all 4 questions are to be attempted.

- (2) All sub-questions of the same question should be answered at one place only in their serial orders, and not scattered.

- (3) Assume suitable data with justification if missing.

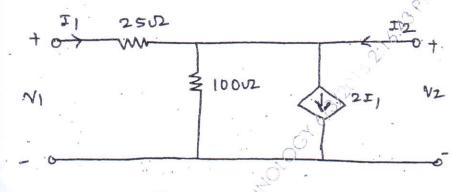

- Determine Y parameters for the network shown in fig 1 (a)

Fig 1 (a)

- Test if  $F(s) = S^4 + S^3 + 5S^2 + 3S + 4$  is a Hurwitz polynomial.

- Two coils connected in series have self inductance 80 mH & 20 mH respectively

The total inductance of the circuit is found to 140 mH. Determine the

- (i) mutual inductance between two coils and

- (ii) The coefficient of coupling

- Synthesize the following function into a network.

$$z(s) = \frac{s^2 - 2s + 2}{s^2 + s + 1}$$

using cauer -1 form.

[ TURN OVER ]

2

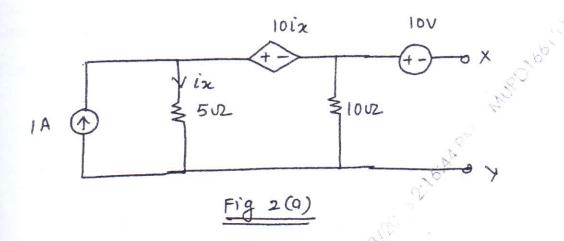

2 (a) Find the Thevenin's equivalent across the terminals XY for the circuit shown in fig 2 (a)

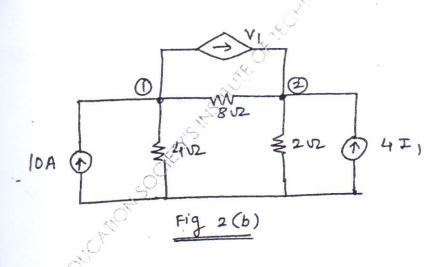

(b) Determine the node voltage at node (1) & (2) of the Network Shown in fig 2(b) by using nodal analysis.

5

5

(c) Test Whether

$F(s) = \frac{s(s+3)(s+5)}{(s+1)(s+4)}$  is a positive real function.

3 (a) Synthesize the driving point function using Foster -I and Foster -II form.

10

$$z(s) = \frac{2(s^2+1)(s^2+9)}{s(s^2+4)}$$

(b) State and prove Initial value theorem.

5

(c) A Transmission line has distributed parameters R=6 Ohms / km, L= 2.2 mH/km C=0.005  $\mu$ F /km & G = 0.005  $\mu$  mho/km

5

Determine characteristics impedance and propagation constant at 1KHz frequency.

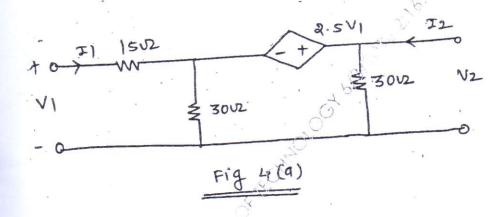

(a) Find ABCD parameters for the two port Network shown in fig 4 (a)

10

5

Find the Network functions  $V_1$ ,  $V_2$ ,  $V_2$ ,  $V_2$  for the network shown in fig 4 (b)

[TURN OVER]

Transmission line has a characteristics impedance of 50+j  $100 \Omega$  and is eminated in a load impedance of 73 - j 42.5 \( \Omega\) Calculate

- (a) The reflection coefficient.

- (b) The standing wave ratio

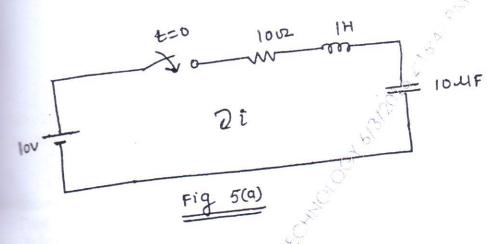

The Network shown in fig 5 (a), switch K is closed at t = 0, Assume all initial

10

tions

as zero. Find i,

$$\frac{di}{dt} & \frac{d^2i}{dt^2}$$

at  $t = 0^+$

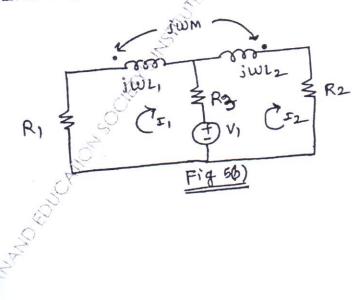

(b) Write the KVL equations in standard form for the N/W shown in fig 5(b)

5

[TURN OVER]

5

5

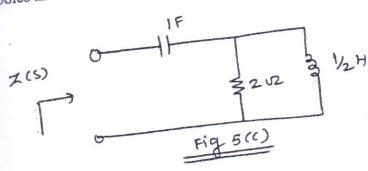

poles and zero of the Impedance Z(s) for the Network Shown in fig 5 (c)

- Why is the Impedance matching required? Draw the following normalized quantities 10 on the smith chart.

- (i) (3+i3) Ω

- $(1.0) \Omega$ (ii)

- (iii) (2-j1)  $\Omega$

- j 1.0 Ω (i)

- (a) Write short note on:

Time domain analysis using Laplace Transform.

- (c) Define the following terms

- (i) Phase Velocity

- (ii) Characteristic impedance

- (iii) Reflection coefficients

E.I.M.

MAY 16

## **QP Code: 30714**

[ Total Marks: 80 (3 Hours) **N. B.**: (1) Question No.1 is compulsory. (2) Out of remaining question, attempt any three questions. (3) Assume suitable additional data if required. (4) Figure to the right of question indicates full marks. (5) Write your answers in ink only. 20 Attempt any four: (a) Explain Alternate mode and Chop mode in a dual trace oscilloscope. (b) What is cold junction compensation in thermocouples. (c) Write a note on piezoelectric transducer. (d) Which is fastest ADC and why? (e) Define accuracy, precision and sensitivity with suitable example. (f) Compare Analog instrument with Digital Instrument. Explain the principle, working and construction of LVDT. What is meant 10 by residual voltage? Draw neat block diagram of Dual Beam Oscilloscope. Give the 10 comparison between Dual Trace and Dual Beam Oscilloscope. What are the various D/A Converting Techniques? Explain any one 10 technique. What is the basic principle of wave analyser? Explain heterodyne type 10 wave analyser with application. Explain Kelvin's double bridge and its application in very low resistance 10. measurement. Draw and discuss Hey Bridge and its application for measurement of 10 inductance. Explain the principle and working of operation of dual slope DVM. 10 Define Q factor and explain working of a Q meter for Q factor 10 measurement. 5 Draw block diagram for generalised measurement system and explain its components. 5 List various sensors for pressure and temperature along with their 5 Brief out classification of errors in measurements. 5 Explain electrodynamometer type watt meter.